Note: the SDCoC voucher bundle is now retired. The WebPACK edition of the Vivado Design Suite is available and does not require a paid license.

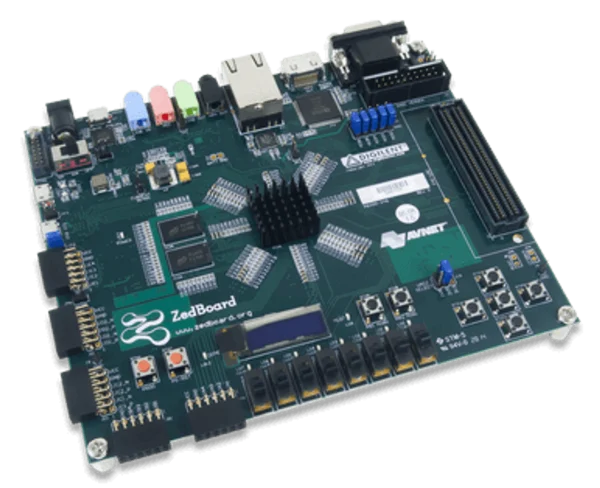

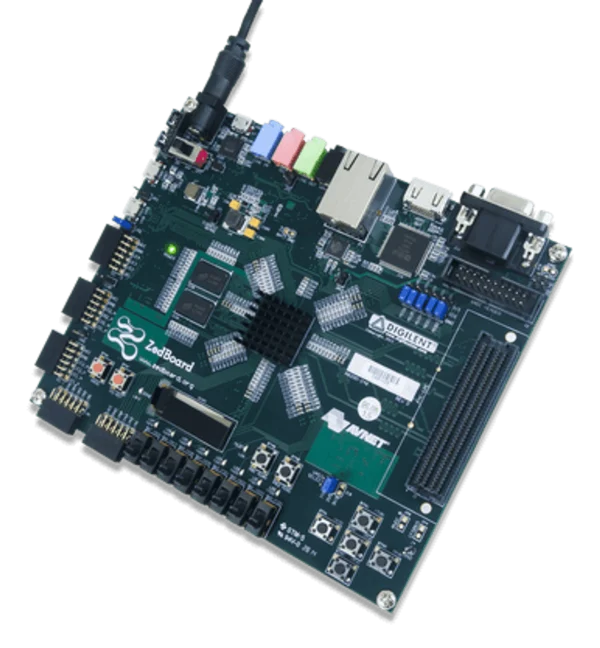

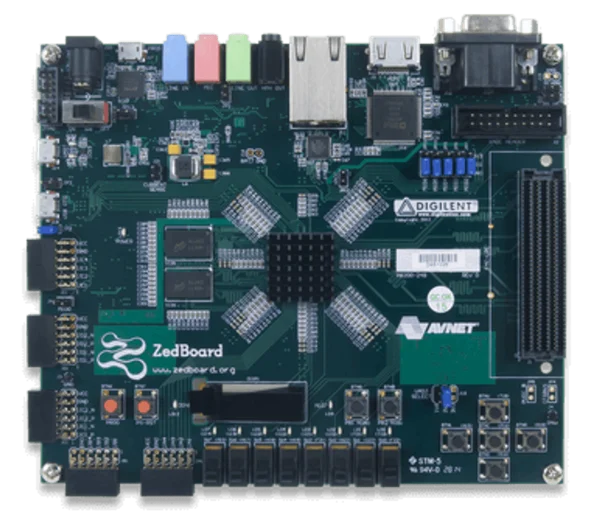

The ZedBoard is a low-cost development board for the Xilinx Zynq-7000 all programmable SoC (APSoC), and a perfect option for those looking to buy a Xilinx FPGA board. Check out our blog post What is Zynq? for more information on Zynq FPGA technology.

Take advantage of the Xilinx Zynq-7000 APSoCs tightly coupled ARM® processing system and 7-Series programmable logic to create unique and powerful designs with the ZedBoard. This ARM board contains everything necessary to create a Linux®, Android®, Windows®, or other OS/RTOS based design. Additionally, several expansion connectors expose the processing system and programmable logic I/Os for easy user access.

Target applications for this Xilinx 7 series FPGA board include video processing, reconfigurable computing, motor control, software acceleration, Linux/Android/RTOS development, exploring RISC processors (ARM), and general Zynq-7000 AP SoC prototyping.

The ZedBoard is supported by Xilinx’s Vivado Design Suite, including the free WebPACK version.

Features:

Xilinx Zynq-7000 AP SoC XC7Z020-CLG484

Dual-core ARM Cortex™-A9 processor

512 MB DDR3

256 MB Quad-SPI Flash

On-board USB-JTAG Programming

10/100/1000 Ethernet

USB OTG 2.0 and USB-UART

Analog Devices ADAU1761 SigmaDSP® Stereo, Low Power, 96 kHz, 24-Bit Audio Codec

Analog Devices ADV7511 High Performance 225 MHz HDMI Transmitter (1080p HDMI, 8-bit VGA, 128×32 OLED)

PS & PL I/O expansion (FMC, Pmod, XADC)

What’s Inluded:

ZedBoard APSoC development board

Custom Digilent cardboard box with protective foam

12 V AC/DC power supply (US, UK & EU adapters)

4 GB SD Card

USB A to micro-B cable

USB Adapter: Male Micro-B to Female Standard-A

Reviews

There are no reviews yet.